# Power Analysis and Validation of Digital Circuits Based on FPGA

# 'Alka Shukla, "Suvarna Mujumdar

#### Abstract

This paper proposes a model for estimation of total power and area of circuits implemented using FPGA's. The family of FPGA being used is Spartan 3. Estimation done by these models helps digital circuit targeted FPGA's, to design well-organized in terms of area, power and speed. This will be helpful for system level designer to provide reasonably correct hardware-related power estimates to guide the algorithm design process. Proposed model is designed in MATLAB by using curve fitting or regression analysis. To develop the model, synthesis of different configurations of multiplier circuits is done using FPGA's which are from Spartan 3 family. Different power standards and number of slices calculated from these different configurations has been used in curve fitting and regression analysis to design the model. Error is minimized to less than 10% for the proposed model.

#### Keywords

FPGA, power dissipation, power, clock gating, IP core, regression analysis, design space exploration

#### I. Introduction

In spite of the proceeded with lessening in power supply voltage, power dissipation will keep on increasing as the operating frequencies. In the event that the power dissipation of a circuitis high, the cost increments. The chip may require unique packaging [1]. The PCB cost additionally increments since the chip may require heat sinks or a fan and so on [2]. The space required on the Board likewise increments. If it is a portable hardware then the battery life decreases. So it is ideal to bring down power dissipation [3]. So other than logic and timing enhancement, now a day's power enhancement is likewise utilized in configuration stream of advanced frameworks [4]. The power optimization can be utilized at any phase of design cycle. At building level, more complex systems are there, which gives more extension to reduction in power. Unquestionably, this decrease in power accomplished because of timing, area, or testability of the design. Voltage, power dissipation and frequency are connected parameters.  $P = C.V^2.F$

From the above equation it is clear that whenever there is a transition, power is dissipated. The power optimization technique applied here is clock gating.

FPGA architectures can be reconfigured according to the parameters specified by the users. High performance can be achieved at low cost. The recent FPGAs have upto 500 MHz clock frequency and millions of gates, fast I/O interface and bigger on-chip memory. As a result they are an easy and cost effective way of implementation. However, the developers still prefer use the languages like C or MATLAB to validate and test their algorithms. One way of filling the gap is to use an easy method for translating the high level algorithm description onto an FPGA platform by using the parameterizable Intellectual Property (IP) cores [5]-[15]. When IP core based designed are used, it reduces the time and effort for a hardware development.

In this work certain IP corebased design like a multiplier are used. These multiplier circuits are designed using VHDL and the power is analysed using Xilinx tool. Different readings of power are noted from the XPower analyser in Xilinx. These readings of power and some other parameter are used to form an equation using curve fitting and regression analysis in MATLAB. These equation are then used in MATLAB to calculate the total power and hence validate the results with that of XPower analyser results. By comparing and validating these results, estimated error can be found.

#### **II. Work Flow**

The proposed work is a model for estimation of total power and area of circuits implemented using FPGA's for Spartan 3 family. Estimation done by these models helps digital circuit targeted FPGA's, to design well-organized in terms of area, power and speed. This will be helpful for system level designer to provide reasonably correct hardware-related power estimates to guide the algorithm design process.

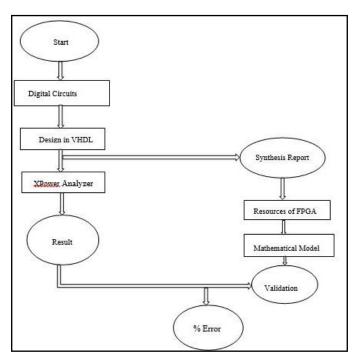

The work flow for the proposed work says that it will start with the choice of digital circuits to be analyzed in the XPower analyzer. The decided circuits will be then designed in VHDL. The power of these circuits designed in VHDL will now be analyzed in XPower analyzer.

The result of XPower analyzer is stored for future reference. Then with the resources of FPGA i.e. slices, CLBs etc., an algorithm will be formed on the existing mathematical models in MATLAB.

The power calculated with these mathematical models and the XPower analyzer willbe compared and thus the error will be minimized. The block by block workflow of the proposed work is defined here in which each block shows the stepwise function of the proposed work.

The procedure of calculating the power of the digital circuits in the XPower analyzer is to choose a benchmark circuit in the FPGA. For that, first of all an FPGA family is chosen.

In this case it is Spartan 3 and under this family there are many packages, one of which can be chosen for this work which is suitable to provide the base paper level of power in mW. Fig. 1 illustrates the workflow of the proposed work where each block shows the stepwise function of the proposed work.

Fig. 1: Work Flow

## III. ISIM Results And RTL Schematic of 64×64 Multiplier

Clock gating is a popular technique used in many synchronous circuits for reducing dynamic power dissipation. Clock gating saves power by adding more logic to a circuit to prune the clock tree. Pruning the clock disables portions of the circuitry so that the flip-flops in them do not have to switch states. Switching states consumes power.

When not being switched, the switching power consumption goes to zero, and only leakage currents are incurred. Clock gating works by taking the enable conditions attached to registers, and uses them to gate the clocks. Therefore, it is imperative that a design must contain these enable conditions in order to use and benefit from clock gating. This clock gating process can also save significant die area as well as power, since it removes large numbers of muxes and replaces them with clock gating logic

#### (a) Without Clock Gtaing

First of all a VHDL code is generated by choosing the type of FPGA, number of I/O ports, clock used or not and other factors. The vector length is then chosen in the benchmark circuit parameters,  $64 \times 64$ in this case. Clock signal 'ce' is disabled by making it a comment in the code. This code is then synthesized and power is analysed using inbuilt XPower analyser. To simulate the behavioural model, a test bench is generated and using ISim simulator it is simulated to give a timing diagram. RTL Schematic can also be obtained which is a view of the arrangement of the circuit. Fig. 2 shows the ISim result of  $64 \times 64$  Multiplier without clock gating

Fig. 2: ISim result of 64×64 Multiplier without clock gating.

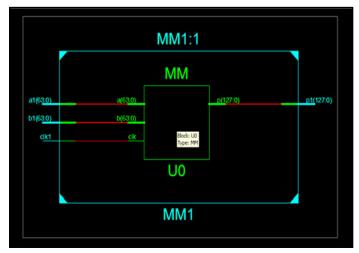

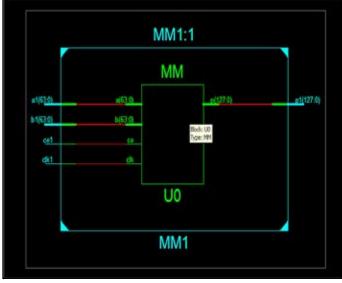

Fig 3 shows the RTL schematic of  $64 \times 64$  multiplier without clock gating.

Fig 3: RTL schematic of 64×64 multiplier without clock gating

#### (b) With Clock Gtaing

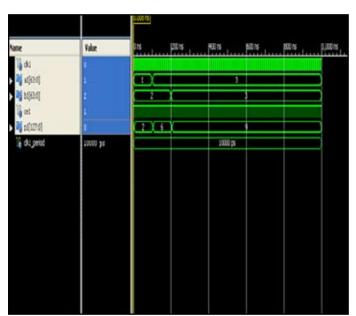

When clock gating is applied the power dissipation is reduced to some extent. In the case of  $64 \times 64$  Multiplier without the clock gating the power analyzed is 1115 mW and with clock gating it is analyzed as 1111mW. So it is visible that power is optimized. Fig. 4 and Fig.5 shows ISim results and RTL Schematicof  $64 \times 64$  Multiplier with clock gating respectively.

Fig. 4: ISim result of 64×64 Multiplier with clock gating.

Fig 5: RTL schematic of 64×64 multiplier with clock gating

# IV. Simulated Results and Validation

# (a) Simulated Result of XPower analyser

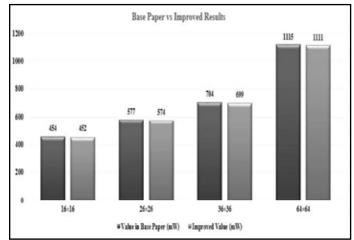

Multipliers of different vector lengths are analysed in XPower analyser and their power is estimated without applying the clock gating technique of power optimization. The same multipliers are analysed again in XPower analyser but now with the power optimization technique called clock gating. We can see that the values of power dissipation are considerably reduced when clock gating technique. Fig. 6 shows graphical representation of results of XPower analyser without clock gating and with clock gating.

Fig. 6:XPower analyser results without clock gating and with clock gating.

And below is the tabular form of this

Table 1: XPower analyser without clock gating and with clock gating.

| Multiplier design with<br>different vector lengths | Value of Power Dissipation<br>in Base Paper[1] | Proposed Value of<br>Power Dissipation | Improved Value of<br>Power Dissipation |

|----------------------------------------------------|------------------------------------------------|----------------------------------------|----------------------------------------|

| 16×16                                              | 454 mW                                         | 453 450 mW                             | 452 mW                                 |

| 26×26                                              | 577 mW                                         | 576-572 mW                             | 574 mW                                 |

| 36×36                                              | 704 mW                                         | 703-697 mW                             | 699 mW                                 |

| 64×64                                              | 1115mW                                         | 1114-1110 mW                           | 1111mW                                 |

#### (b) Simulated result of MATLAB

A synthesis report is formed from the results of XPower analyser and the data from this synthesis report is moulded into equations using curve fitting technique in MATLAB. These equations are used to calculate total power. The results of MATLAB synthesis are compared to the results of XPower analyser and hence validated. Estimated error is calculated with a formula

% Error = {(Synthesis value – Estimated Value) ÷ (Estimated Value)} × 100

Table 2 shows the comparision between the results of XPower analyser and power calculated in MATLAB.

Table 2: Validation Result comparison and error estimation

| CIRCUIT<br>Multiplier | POWER in mW |        |       | NO.ofCOMPONENTS |    |      | POWER in mW       |              |             |                | ERROR         |        |

|-----------------------|-------------|--------|-------|-----------------|----|------|-------------------|--------------|-------------|----------------|---------------|--------|

|                       | Logic       | Signal | Clock |                 |    |      | No. of<br>OP pins | I/P<br>power | OP<br>nower | Total<br>power | Est.<br>Power | %Error |

| 8×8                   | 0           | 1      | 4     | 16              | 1  | 17   | 16                | 0.45         | 82.75       | 365            | 364.6574      | 0.09%  |

| 16×16                 | 0           | 2      | 3     | 32              | 1  | 33   | 32                | 0.69         | 165.5       | 451            | 450.3367      | 0.15%  |

| 24×24                 | 1           | 6      | 4     | -53             | 4  | - 49 | 48                | 0.91         | 248.25      | 544            | 536.3219      | 1.40%  |

| 32×32                 | 2           | 9      | -4-   | 73              | -4 | 65   | 61                | 1.15         | 331         | 633            | 622.6762      | 1.63%  |

| 40×40                 | 4           | 18     | 4     | 159             | 9  | 81   | 80                | 137          | 413.75      | 732            | 719.272       | 1.74%  |

| 48×48                 | 5           | 23     | 4     | 182             | 9  | 97   | 96                | 1.59         | 496.49      | 823            | 806.1326      | 2.04%  |

| 56×56                 | 8           | 42     | 4     | 332             | 16 | 113  | 112               | 1.83         | 579.24      | 934            | 913.1701      | 2.23%  |

| 64×64                 | 10          | -51    | 4     | 387             | 16 | 129  | 128               | 2.05         | 661.99      | 1030           | 1005.4        | 2.30%  |

It can be seen that the % error is quite less. It is reduced to less than 10%.

## V. Conclusion

Study of the internal architecture of FPGA and exploration of various blocks present in it. The work is an extensive literature survey related to low power techniques that can be applied at different hierarchy levels in the design to implement low power digital circuits. The various estimation models that are required for validation purpose are also founded.Proposed model is designed in MATLAB by using curve fitting or regression analysis. To develop the model synthesis of different configuration of multiplier circuits using FPGA's from Spartan 3 family is to be done. Different power standards and number of slices calculated from these different configurations has been used in curve fitting and regression analysis to design the model. Error is minimized to less than 10% for the proposed model.

## References

- [1] Bojan Javanovic, Ruzica Jevtic and Carlos Carreras, "Binary Division Power Models for High-Level Power Estimation of FPGA-Based DSP Circuits", IEEE Transactions of Industrial Informatics, vol.10, no. 1, pp 393-398,2014.

- [2] Ian Kuon and Jonathan Rose, "Measuring the gap between FPGAs and ASICs", IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 26, no. 2, pp 203-215,2007.

- [3] K.N.Vijeyakumar, V.Sumathy, A. Dinesh Babu, S. Elango and S. Saravanakumar, "FPGA implementation of low power hardware efficient flagged binary coded decimal adder", International Journal of Computer Applications, vol. 46, no. 14, pp 41-45, 2012.

- [4] S. Kanaga and S. Thilakavathi, "Performance optimization using delay padding strategy in FPGA's, International Journal of Advanced Research in Electronics and Communication Engineering (IJARECE)", vol.3, no. 2, pp 127-130,2014.

- [5] Sudip. K. Nag and Rob A. Rutenbar, "Performance-driven simultaneous placement and routing for FPGA's", IEEE Transactions on Compute Aided Design of Integrated Circuits and Systems, vol. 17, no. 6, pp 499-518,1998.

- [6] A. Chandrakasan, S. Sheng, R. W. Brodersen, 1992, "Lowpower CMOS digital design", IEEE Journal of Solid-State Circuits, vol.27, no. 4, pp.473-484, 1992.

- [7] Prithviraj Banerjee, Malay Haldar, Anshuman Nayak, Victor Kim, Vikram Saxena, Steven Parkes, Debabrata Bagchi, Satrajit Pal, Nikhil Tripathi, David Zaretsky, Robert Anderson, and Juan Ramon Uribe, 2, "Overview of a Compiler for Synthesizing MATLAB Programs onto FPGAs", IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 12, no. 3, pp 312-324,2004.

- [8] Rolf Enzler, Tobias Jeger, Didier Cottet, and Gerhard Troster, "High-Level Area and Performance Estimation of Hardware Building Blocks on FPGAs", Proceedings of International Workshop on Field-Programmable Logic and Applications, vol. 1896, pp 525-534, 2000.

- [9] Lian Fang and David C Gossard, "Multidimensional curve fitting to unorganized data points by nonlinear minimization", Computer-Aided Design, vol. 27, no. 1, pp 48-58,1995

- [10] J. L. Earnshaw and I. M Yuille, "A Method of Fitting Parametric Equations for Curves and Surfaces to Sets of Points Defining Them Approximately", Computer- Aided Design, vol.3, no. 2, pp 19-22, 1971.

- [11] Ruzica Jevtic and Carlos Carreras, "Power Estimation of Embedded Multiplier Blocks in FPGAs", IEEE Transactions on Very Large Scale Integration (VLSI) System, vol. 18, no. 5, pp 835-839, 2010.

- [12] Pietro Babighian, Luca Benini and Enrico Macii, "A Scalable Algorithm for RTL Insertion of Gated Clocks Based on ODCs Computation", IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 24,

no.1, pp 29-42, 2005.

- [13] Supamas Sirichotiyakul, Tim Edwards, Chanhee Oh, Rajendran Panda and David Blaauw, "An Accurate Leakage Estimation and Optimization Tool for Dual-Vt Circuits", IEEE Transactions On Very Large Scale Integration (VLSI) Systems, vol. 10, no. 2, pp 79-90,2002.

- [14] Kara K.W. Poon, Andy Yan and Steven J.E. Wilton, "A Flexible Power Model for FPGAs", Proceedings of International Conference on Field-Programmable Logic and Applications, vol. 2438, pp 312-321, 2002.

- [15]] N. E. Zergainoh, Ludovic Tambour, Pascal Urard and Ahmed Amine Jerraya, "Macrocell Builder: IP-Block-Based Design Environment for High-Throughput VLSI Dedicated Digital Signal Processing Systems", EURASIP Journal on Advances in Signal Processing, vol. 2006, no. 14, pp 1-11, 2006.

#### **Author Profile**

Alka Shuklawas born in Rajouri, J&K. India. She has completed his secondary and higher secondary examination with science stream in 2005 and 2007 respectively. She has completed his schooling from Model Institute of Education and Research, Jammu, J&K.She received the B.Tech degree in Electronics & Communication Engineering, from Greater Noida Institute Of Technology, Greater Noida, U.P.She is

pursuing M.Tech in Electronics & Communication Engineering from Ajay Kumar Garg Engineering College, Ghaziabad, U.P. (2014-2016). Her current interest includes power analysis of digital circuits based on FPGA.

Suvarna Mujumdar was born in Indore, Madhya Pradesh, India in 1981. She received B.E. in Electronics and Communication Engineering from RGPV University, Bhopal in 2003 and M.Tech degree in Electronics and communication Engineering from UPTU, Lucknow in 2014. She started her teaching career in 2003 and is currently working as an Assitant Professor in Ajay Kumar Garg

Engineering College, Ghaziabad. Her main areas of research interest are Wireless Communication and Embedded Systems.